## Characteristics of solid-phase diffused ultra-shallow junction using phosphorus doped silicon oxide films for fabrication of sub-100 nm SOI MOSFET

WON-JU CHO, KIJU IM, JONG-HEON YANG, JIHUN OH, SEONGJAE LEE Fundamental Technology Department, Basic Research Lab., ETRI, 161, Gajeong-dong, Yuseong-gu, Daejon 305-360, Korea E-mail: chowj@etri.re.kr

## KYOUNGWAN PARK

Department of Nano Science & Technology, University of Seoul, 90 Cheonnong-dong, Dongdaemun-gu Seoul, 130-743 Korea

Strenuous efforts are being focused on further scaling of metal-oxide-semiconductor field-effect transistors (MOSFETs) into the sub-100 nm regime. Complementary MOS devices (CMOS) fabricated on silicon-oninsulator (SOI) wafers have attracted a lot of attention because of the advantages of full dielectric isolation and reduced junction capacitance over those on bulk silicon wafers in regard to integrated circuit (IC) applications for low stand-by power and high performance. Moreover, the fabrication technique involved in SOI MOSFET can remove or relax some of the process and material constraints on the MOS-FET scaling, because it provides a low leakage current, latch-up elimination, high soft error immunity, smaller subthreshold swing, and a simple device structure and process. However, one of the major challenges to overcome is the ultra-shallow junction formation method, which prevents short channel effects for deep sub-100 nm devices [1, 2]. The conventional approach for junction formation is ion implantation with low-energy ion beams. The crystal defects associated with the energetic ion beam bombardment are unavoidable and act as the primary source of junction leakage currents. The junction leakage degrades the device performance and leads to an increase in power consumption. Therefore, an alternative method is required to make use of the advantages of the SOI devices. Doping using solid-phase diffusion (SPD) is an effective method to form damage-free ultra-shallow junctions.

In this paper, we report the doping properties of the SPD method and the electrical characteristics of sub-100 nm SOI MOSFETs fabricated using the SPD technique for ultra-shallow source and drain junction formation. The phosphorus doped oxide films used as the SPD source are usually prepared by chemical vapor deposition (CVD), but we used a liquid-state dopant source containing silicon, oxygen and phosphorus. A wafer was coated with the dopant source using a spin coating technique. After baking at 250 °C for 20 min, the liquid source was converted to a solid phosphorus doped silicon oxide layer on the top of the wafer. The refractive index and density of this oxide layer were 1.42 and 2.05 g/cm<sup>3</sup>, respectively. Then the coated wafer was placed in a rapid thermal annealing (RTA) system and a PN junction was created after the phosphorus had diffused into the silicon. In this way,  $N^+P$  junction diodes and SOI MOSFETs were fabricated.

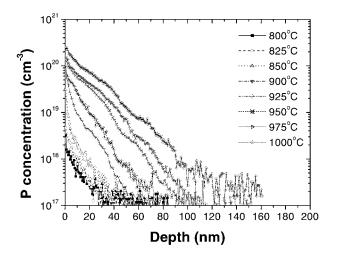

Fig. 1 shows the secondary ion mass spectrometry (SIMS) depth profile of phosphorus for various RTA process temperatures. The RTA process was performed for 30 s in N<sub>2</sub> ambient. The diffusion depth of the phosphorus increases with RTA temperature. The surface concentration of phosphorus also increased with the RTA temperature due to the enhanced solid solubility of phosphorus atoms. In nano-scale MOSFET devices, a channel impurity concentration of  $10^{18}$  cm<sup>-3</sup> is required to suppress the short channel effect. It is clear that a shallow junction, less than the 50 nm deep, defined at  $1 \times 10^{18}$  cm<sup>-3</sup> can be obtained when the RTA temperature is below 925 °C.

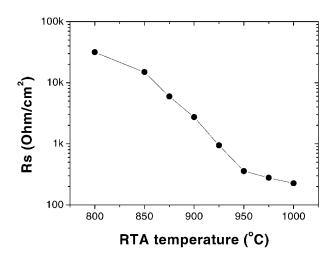

Fig. 2 shows the relationship between the sheet resistance (Rs) measured using the four-point probe and RTA temperature. The Rs monotonically decreases as the RTA temperature and junction depth increase. The Rs is lower than 1 k Ohm/cm<sup>2</sup> at 925 °C, which is the maximum drain extension sheet resistance required for 32 nm-technology [3]. Since the surface dopant concentration increased as the RTA temperature increased, more improvements can be expected with control of RTA duration time.

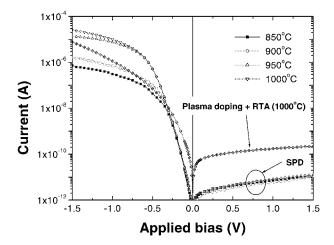

Fig. 3 shows the current-voltage (I-V) characteristics of  $N^+P$  diodes fabricated on SOI substrates by SPD methods. In order to verify the effectiveness of the SPD process, the I-V characteristics of  $N^+P$  diodes fabricated by the plasma doping method, which is often used in ultra-shallow junction formation, are also shown in Fig. 3 for comparison. It is observed that the forward bias current depends on the RTA temperature. As the RTA temperature increased, the forward bias current increased, while the reverse bias current remained almost constant. The increase in forward bias current could be attributed to the reduction of sheet resistance resulting from high temperature RTA. In the case of the plasma doping sample, the forward bias cur-

Figure 1 Depth profiles of P analyzed by SIMS for various RTA temperatures.

Figure 2 Dependence of sheet resistance (Rs) on RTA temperature.

*Figure 3* Current-voltage characteristics of  $N^+P$  diode using SPD method and plasma doping method.

rent is lower and the reverse bias is higher than those of the SPD samples even after annealing at 1000 °C. It is well known that defects generated by ion implantation or plasma doping cannot be completely annealed out [4]. The SPD method does not create the defects during the junction formation. Consequently,

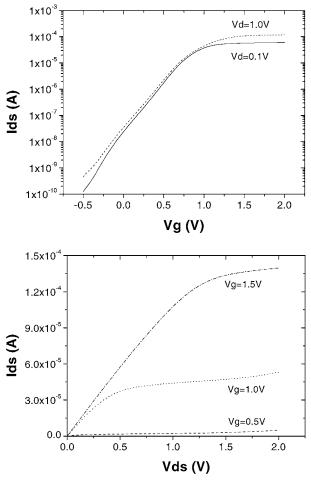

*Figure 4*  $I_{\rm D}$ - $V_{\rm G}$ ,  $I_{\rm D}$ - $V_{\rm D}$  characteristics of SOI MOSFET fabricated by SPD method ( $L_{\rm g} = 0.1 \ \mu \text{m/W}_{\rm ch} = 2 \ \mu \text{m}$ ).

these results clearly show that the SPD process is superior to the plasma doping process for diode formation.

Fig. 4 shows the subthreshold characteristics ( $I_d$ - $V_g$ ) and the measured drain current ( $I_d$ - $V_d$ ) for the SOI N-MOSFET of 0.1 um gate length and 2 um channel width without gate spacer and LDD (lightly doped drain) structure, which was fabricated by the SPD method with 950 °C RTA. It has an excellent subthreshold behavior on/off current ratio. These results confirm that the SOI N-MOSFET fabricated by SPD method with spin coated oxide glass operated successfully, providing a promising doping method to make sub-100 nm MOSFETs.

In summary, the solid-phase diffusion (SPD) method for an ultra-shallow junction formation has been investigated. Sheet resistances of the phosphorus diffused area were below 1 k Ohm/cm<sup>2</sup> when the RTA temperature was higher than 925 °C. The diffusion depth of the phosphorus could be controlled to be below 40 nm with temperatures lower than 925 °C. The diode characteristics of N<sup>+</sup>P junction were improved as the RTA temperature was increased and a comparison study shows that the SPD method is superior to the plasma doping method. SOI N-MOSFETs fabricated by this SPD method operated successfully, demonstrating SPD to be a promising doping technique.

## References

- 1. C. M. OSBURN, I. DE, K. F. YEE and A. SRIVASTAVA, J. Vac. Sci. Technol. B 18 (2000) 337.

- 2. C. R. CLEAVELIN, B. C. COVINGTON and L. A. LARSON, *ibid.* **18** (2000) 346.

- "International Technology Roadmap for Semiconductors 2001 Edition" (Semi Conductor Industry Association, San Jose, CA95110).

- M. M. OKA, A. NAKADA, K. TOMITA, T. SHIBATA, T. OHMI and T. NITTA, *Jpn. J. Appl. Phys.* 34 (1995) 796.

Received 3 September and accepted 1 October 2003